## Towards a high degree of uniformity in the diameter and length of self-catalyzed GaAs nanowires on silicon by adjusting the growth temperature

A. M. Raya<sup>1</sup>, D. Fuster<sup>1</sup>, J. M. Llorens<sup>1</sup>, J. Buencuerpo<sup>1</sup> and J. M. Ripalda<sup>1</sup>

<sup>1</sup>Instituto de Microelectrónica de Madrid, CSIC, 28760, Tres Cantos, Madrid, Spain andres.raya@csic.es

## Abstract

Nanowire-based devices are promising candidates for next generation solar cells. Lattice matching enforces a significant restriction on material choices for multijunction solar cells. However, the strain relaxation through the nanowire sidewall allows the growth of lattice-mismatched III-V compounds on inexpensive silicon substrates. Our theoretical calculations based on the detailed balance limit [1,2] indicate that an optimal tandem cell based on GaAs nanowires on Si can achieve an efficiency of 38.8%. The efficiency reaches a maximum value of 44.9% if an  $AI_{0.24}Ga_{0.76}As$  compound ( $E_g = 1.72 \text{ eV}$ ) is used for the nanowire top cell, making III-V nanowire on Si tandem cells a promising candidate to compete with current three- and four-junction solar cells.

Many parameters need to be tuned for an optimum growth of the nanowires by molecular beam epitaxy (MBE). The understanding and control of the nanowire growth process is necessary in order to design and build a high efficiency device. The thickness of the  $SiO_2$  layer formed on the silicon substrate plays a critical role in the density and yield of self-catalyzed GaAs nanowires [3], whereas the length and diameter of the nanowires have to be optimized because they affect the current matching [4]. In the present work we investigate the influence of the growth temperature on the final characteristics of the nanowires. We report that the optimization of the substrate temperature used during the Ga droplet formation step leads to a significant narrowing of the diameter and length distributions of the nanowires.

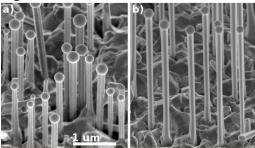

Series of samples consisting of GaAs nanowires on Si (111) substrates were grown using standard growth parameters, whereas the growth temperature was set to different values in the interval between 555 and 630 °C. We have used scanning electron micrographs of the samples to measure the density, yield, diameter and length of a wide number of nanowires as functions of the oxide thickness and growth temperature. The results reveal that lowering the growth temperature leads to a higher degree of uniformity in the length and diameter of the GaAs nanowires, as can be seen in Fig. 1. This tendency is observed regardless of whether we are using an optimum value of the native  $SiO_2$  layer or a thicker one. Optical microscopy and reflectivity results are also correlated with electron microscopy images.

## References

[1] W. Shockley and H. J. Queisser, J. Appl. Phys., 32, 510 (1961)

[2] A. De Vos, J. Phys. D.( Appl. Phys.), **13**, 839 (1980)

[3] F. Matteini, G. Tütüncüoglu, H. Potts, F. Jabeen and A. Fontcuberta i Morral, Cryst. Growth Des., **15**, 3105 (2015)

[4] N. Huang, C. Lin and M. L. Povinelli, J. Appl. Phys., 112, 064321 (2012)

## Figures

**Figure 1:** SEM images of GaAs nanowires grown on Si (111) substrate using a)  $T_{growth} = 630^{\circ}$ C and b)  $T_{growth} = 580^{\circ}$ C. Scale bar corresponds to 1 um.